# CHERI: Architectural support for strong memory safety and scalable compartmentalized software

**Robert N. M. Watson**, Simon W. Moore, Peter Sewell, Peter G. Neumann, Brooks Davis

Hesham Almatary, Ricardo de Oliveira Almeida, Jonathan Anderson, Alasdair Armstrong, Rosie Baish, Peter Blandford-Baker, John Baldwin, Hadrien Barrel, Thomas Bauereiss, Ruslan Bukin, Brian Campbell, David Chisnall, Jessica Clarke, Nirav Dave, Lawrence Esswood, Nathaniel W. Filardo, Franz Fuchs, Dapeng Gao, Ivan Gomes-Ribeiro, Khilan Gudka, Brett Gutstein, Angus Hammond, Graeme Jenkinson, Alexandre Joannou, Mark Johnston, Robert Kovacsics, Ben Laurie, Ka Wing Li, Zhuo Ying Jiang Li, Jessica Man, A. Theo Markettos, J. Edward Maste, Alfredo Mazzinghi, Alan Mujumdar, Prashanth Mundkur, Steven J. Murdoch, Edward Napierala, George Neville-Neil, Kyndylan Nienhuis, Robert Norton-Wright, Philip Paeps, Lucian Paul-Trifu, Allison Randal, Ivan Ribeiro, Alex Richardson, Michael Roe, Colin Rothwell, Peter Rugg, Hassen Saidi, Thomas Sewell, Stacey Son, Ian Stark, Domagoj Stolfa, Andrew Turner, Munraj Vadera, Konrad Witaszczyk, Jonathan Woodruff, Hongyan Xia, Vadim Zaliva, and Bjoern A. Zeeb

SRI International

Capabilities Limited

University of Cambridge

Rennes – 12 September 2025

### Approved for public release; distribution is unlimited.

CHERI development was supported by the Defense Advanced Research Projects Agency (DARPA) and the Air Force Research Laboratory (AFRL), under contract FA8750-10-C-0237 ("CTSRD"), with additional support from FA8750-11-C-0249 ("MRC2"), HR0011-18-C-0016 ("ECATS"), FA8650-18-C-7809 ("CIFV"), HR001122C0110 ("ETC"), HR001123C0031 ("MTSS"), and FA8750-24-C-B047 ("DEC") as part of the DARPA I2O CRASH, I2O MRC, MTO SSITH, and I2O CPM research programs. The views, opinions, and/or findings contained in this report are those of the authors and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

Arm's Morello and portions of the Morello-enabled software stack were supported by the Innovate UK project 105694 ("Digital Security by Design (DSbD) Technology Platform Prototype"), Innovate UK project 107145 ("Assessing the Viability of an Open-Source CHERI Desktop Software Ecosystem"), Innovate UK project 10027440 ("Developing and Evaluating an Open-Source Desktop for Arm Morello"), and Innovate UK project 10027332 ("MOJO - A Robust Java Virtual Machine for Morello").

We further acknowledge EPSRC REMS (EP/K008528/I), EPSRC CHaOS (EP/V000292/I), ERC ELVER (789108), the Isaac Newton Trust, the UK Higher Education Innovation Fund (HEIF), Thales E-Security, Microsoft Research Cambridge, Arm Limited, Google, Google DeepMind, HP Enterprise, and the Gates Cambridge Trust.

### Introduction

- CHERI is a new processor technology that mitigates software security vulnerabilities

- Developed by the University of Cambridge and SRI International starting in 2010, supported by DARPA

- Arm collaboration from 2014 supported by DARPA

- Arm Morello prototype processor, shipped 2022 supported by UKRI

- CHERI-RISC-V due for ratification by RISC-V International mid-2025; multiple {IP, ASIC} products announced for 2025-2026

- Today's talk:

- What is CHERI and how does it change software security?

- Transition efforts including Arm, Google, Microsoft, and beyond ...

- http://www.cheri-cpu.org/

- Watson, et al., CHERI: Hardware-Enabled C/C++ Memory Protection at Scale, IEEE Security and Privacy Magazine, July-August 2024.

An early experimental FPGAbased CHERI tablet prototype running the CheriBSD operating system and applications, Cambridge, 2013.

High-performance Arm Morello chip able to run a full CHERI software stack, Cambridge, 2022

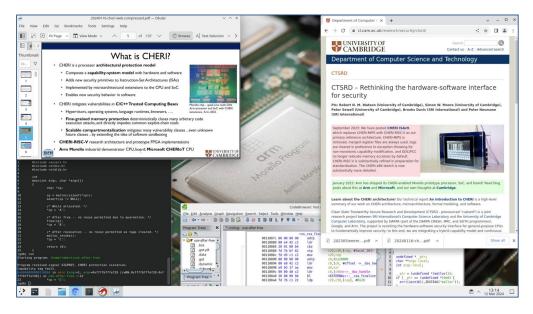

### What is CHERI?

- CHERI is a processor architectural protection model

- Composes a capability-system model with hardware and software

- Adds new security primitives to Instruction-Set Architectures (ISAs)

- Implemented by microarchitectural extensions to the CPU and SoC

- Enables new security behavior in software

- CHERI mitigates vulnerabilities in C/C++ Trusted Computing Bases

- Hypervisors, operating systems, language runtimes, browsers, ....

- **Fine-grained memory protection** deterministically closes many arbitrary code execution attacks, and directly impedes common exploit-chain tools

- Scalable compartmentalization mitigates many vulnerability classes .. Even unknown future classes .. by extending the idea of software sandboxing

- There are now multiple industrial implementations (Arm, Microsoft, Codasip, ...)

Morello chip – 7nm quad-core multi-GHz Arm processor and SoC with CHERI extensions, Arm, 2022.

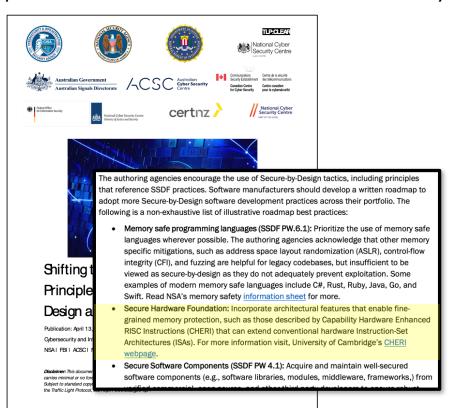

### CHERI has featured in recent policy discussions about memory safety

April 2023 February 2024

The chip, in particular, is an important hardware building block to consider. There are several promising efforts currently underway to support memory protections through hardware. For example, a group of manufacturers have developed a new memory-tagging extension (MTE) to cross-check the validity of pointers to memory locations before using them. If they are invalid, the CPU produces an error. This technique is an effective method to detect memory safety bugs, but this approach should not be considered a comprehensive solution to prevent all memory safety exploits. This architecture method is the Capability Hardware Enhanced RISC Instructions (CHERI). This architecture changes how software accesses memory, with the aim of removing vulnerabilities present in historically memory unsafe languages.

### **HARDWARE-SOFTWARE CO-DESIGN FOR CHERI**

### Architectural primitives for software security

**Applications**

Systems software

Compilers and toolchain

Instruction-Set Architecture (ISA)

Microarchitecture

Software configures and uses capabilities to continuously enforce safety properties such as **referential**, **spatial**, **and temporal memory safety**, as well as higher-level security constructs such as **compartment isolation**

CHERI capabilities are an architectural primitive that compilers, systems software, and applications use to constrain their own future execution

The microarchitecture implements the capability data type and tagged memory, enforcing invariants on their manipulation and use such as capability bounds, monotonicity, and provenance validity

### Hardware-software-semantics co-design

- Hardware-software-semantics co-design + concrete prototyping:

- Portable CHERI abstract protection model

- Concrete ISA instantiations in 32/64-bit RISC-V (+ Microsoft CHERIOT), 64-bit Armv8-a (Morello)

- Formal ISA models, QEMU-CHERI, Morello and FPGA prototypes

- Formal proofs that ISA security properties are met, automatic testing of simulators and implementations

- CHERI Clang/LLVM/LLD, CheriBSD, C/C++-language applications

- Repeated iteration to improve {performance, security, compatibility, ...} as evaluated through multi-million LoC studies

- Co-design includes extensive engagement with industrial partners such as Arm, Google, and Microsoft, as well as RISC-V community

### CHERI ISA refinement over 14 years

Technical Report

UCAM-CL-TR-987

Number 987

Computer Laboratory

Capability Hardware **Enhanced RISC Instructions:** CHERI Instruction-Set Architecture (Version 9)

Robert N. M. Watson, Peter G. Neumann, Jonathan Woodruff, Michael Roe, Hesham Almatary, Jonathan Anderson, John Baldwin, Graeme Barnes, David Chisnall, Jessica Clarke, Brooks Davis, Lee Eisen, Nathaniel Wesley Filardo, Franz A. Fuchs, Richard Grisenthwaite, Alexandre Joannou, Ben Laurie, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Kyndylan Nienhuis, Robert Norton, Alexander Richardson, Peter Rugg, Peter Sewell, Stacey Son, Hongyan Xia

September 2023

15 II Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 https://www.cl.cam.ac.uk/

| Year                      | Version         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2010-2012                 | ISAvI           | RISC capability-system model w/64-bit MIPS<br>Capability registers, tagged memory<br>Guarded manipulation of registers                                                                                                                                                                                                                                                                                                                               |

| 2012                      | ISAv2           | Extended tagging to capability registers Capability-aware exception handling Boots an MMU-based OS with CHERI support                                                                                                                                                                                                                                                                                                                                |

| 2014                      | ISAv3           | Fat pointers + capabilities, compiler support<br>Instructions to optimize hybrid code<br>Sealed capabilities, CCall/CReturn                                                                                                                                                                                                                                                                                                                          |

| 2015                      | ISAv4           | MMU-CHERI integration (TLB permissions) ISA support for compressed 128-bit capabilities HW-accelerated domain switching Multicore instructions: full suite of LL/SC variants                                                                                                                                                                                                                                                                         |

| 2016                      | ISAv5           | CHERI-128 compressed capability model<br>Improved generated code efficiency<br>Initial in-kernel privilege limitations                                                                                                                                                                                                                                                                                                                               |

| 2017                      | ISAv6           | Mature kernel privilege limitations Further generated code efficiency Architectural portability: CHERI-x86, CHERI-RISC-V sketches Exception-free domain transition                                                                                                                                                                                                                                                                                   |

| 2019                      | ISAv7           | Architectural performance optimization for C++ applications Microarchitectural side-channel resistance features Architecture-neutral CHERI protection model All instruction pseudocode from a formal model CHERI Concentrate capability compression Improved C-language support, dynamic linking, sentry capabilities Elaborated CHERI-RISC-V ISA 64-bit capabilities for 32-bit architectures Accelerated tag operations for temporal memory safety |

| 2020                      | ISAv8           | MMU temporal memory-safety assist; e.g., capability dirty bit<br>Optimizations for sentry capabilities<br>CHERI-RISC-V privileged support, general maturity<br>Further C-language semantics improvements                                                                                                                                                                                                                                             |

| <sup>2023</sup><br>rdware | ISAv9<br>Enhanc | CHERI-RISC-V now the reference architecture CHERI-RISC-V maturity for standardization, including tag stripping Edraftscopinstructions: CHERI                                                                                                                                                                                                                                                                                                         |

Watson, et al. Capability Ha CHERI Instruction-Set Architecture (Version 9), UCAM-CL-TR-987, September 2023.

Capabilities

RISC

C/C++ and capabilities

In-kernel use

Temporal memory safety

efficiency

Arm Morello

architecture

CHERI-RISC-V architecture

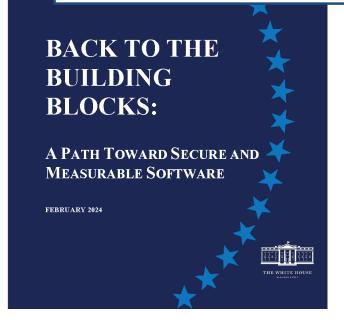

### CHERI research and development timeline

**Years I-2:** Research platform, prototype architecture

Years 2-4: Hybrid C/OS, compartment model

Years 4-7: Efficiency, CheriABI/C/C++/linker, Armv8-A

**Years 8-12:** RISC-V, temporal safety, proofs, Arm Morello, Microsoft CHERIOT lbex

**Years 13-14:** CHERI software ecosystem, library & kernel compartmentalization, commercial products, RISC-V standardization

UNIVERSITY OF CAMBRIDGE

### **CHERI PROTECTION MODEL** AND ARCHITECTURE

### Architectural primitives for software security

**Applications**

Systems software

Compilers and toolchain

Instruction-Set Architecture (ISA)

Microarchitecture

Software configures and uses capabilities to continuously enforce safety properties such as **referential**, **spatial**, **and temporal memory safety**, as well as higher-level security constructs such as **compartment isolation**

CHERI capabilities are an architectural primitive that compilers, systems software, and applications use to constrain their own future execution

The microarchitecture implements the **capability data type** and **tagged memory**, enforcing invariants on their manipulation and use such as **capability bounds**, **monotonicity**, and **provenance validity**

# Capability systems

- The capability system is a design pattern for how CPUs, languages, OSes, ... can control access to resources

- Capabilities are communicable, unforgeable tokens of authority

- In capability-based systems, resources are reachable only via capabilities

- Capability systems limit the scope and spread of damage from accidental or intentional software misbehavior

- They do this by making it natural and efficient to implement, in software, two security design principles:

- The principle of least privilege dictates that software should run with the minimum privileges to perform its tasks

- The **principle of intentional use** dictates that when software holds multiple privileges, it must explicitly select which to exercise

- These two principles are the heart of the CHERI design

The CAP computer project ran from 1970-1977 at the University of Cambridge, led by R. Needham, M. Wilkes, and D.Wheeler.

### CHERI design goals and approach

- De-conflate memory virtualization and protection

- Memory Management Units (MMUs) protect by location (address)

- CHERI protects existing **references** (**pointers**) to code, data, objects

- Reusing existing pointer indirection avoids adding new architectural table lookups

- Architectural mechanism that enforces software policies

- Language-based properties e.g., referential, spatial, and temporal integrity (C/C++ compiler, linkers, OS model, runtime, ...)

- **New software abstractions** e.g., software compartmentalization (confined objects for in-address-space isolation, ...)

### CHERI is a portable model

- CHERI is an abstract architectural protection model; like VM, it is:

- Integrated into the Instruction-Set Architecture (ISA)

- **ISA neutral** (thus far) applied to both 32-bit and 64-bit architectures; e.g., MIPS, RISC-V, Arm-A, Arm-M, and x86 64

- Accommodates diverse microarchitectures (e.g., pipelined, OoO,, ...)

- Has a **portable software model** added to multiple compilers, OSes, etc.

- Various CHERI-enabled software projects aim to start upstreaming support as first production microarchitectures ship over the next 18 months

- Most changes are **CHERI-specific** rather than "CHERI-RISC-V-specific" or "Morello-specific"; e.g., CHERI LLVM, CHERI GDB, CheriBSD, CHERI Linux, CHERI-seL4, ...

- Portions of compiler back ends, debugger targets, OS assembly, etc., are ISA-specific

- While the initial focus for CHERI was on the C/C++ corpus, there is substantial work on using CHERI for other languages and language runtimes; e.g., Rust, OpenJDK, V8

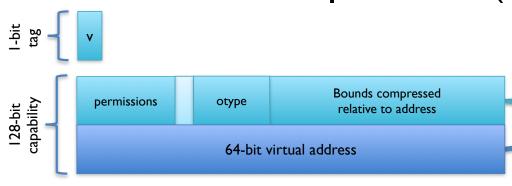

### CHERI 128-bit capabilities (64-bit, MMU-enabled)

Capabilities extend integer memory addresses with protection metadata:

- Out-of-band tags protect capability integrity/derivation in registers + memory

- Dereferencing an invalid capability (tag value of zero) throws an exception

- · Overwriting a capability in memory clears its validity tag

- Bounds and permissions authorize access to memory

- Dereferencing a capability outside of its bounds, permissions, etc., throws an exception

- Sealing implements non-bypassable encapsulation for data and control flow

- Guarded manipulation controls how capability values themselves may be manipulated

- E.g., enforcing provenance validity and monotonicity

CHERI's tag enables

deterministic, secretsfree protection

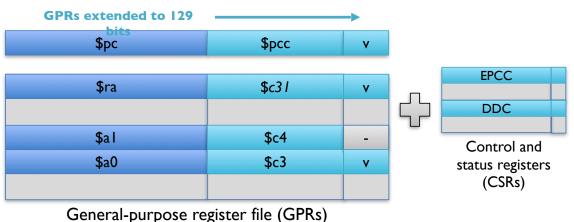

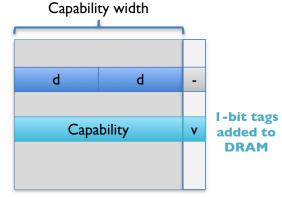

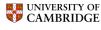

### Capability-extended register file + tagged memory

Physical memory

- 64-bit general-purpose registers (GPRs) extended with 64 bits of metadata and a I-bit validity tag

- Program counter (PC) is extended to be the program-counter capability (\$PCC)

- Tagged memory protects capability-sized and -aligned words in DRAM by adding a I-bit validity tag

- **New instructions** are used to explicitly load, store, inspect, and manipulate capability values

- **Existing encodings** are reused for capability-relative dereferences when in a suitable mode

- **Default data capability (\$DDC)** constrains legacy integer-relative ISA load and store instructions

- **System mechanisms** are extended (e.g., capability-instruction enable control register, new PTE permissions, new exception codes, exception stack pointers + vectors become capabilities, etc.)

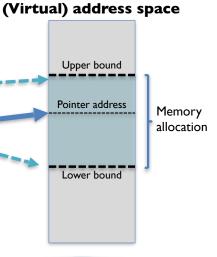

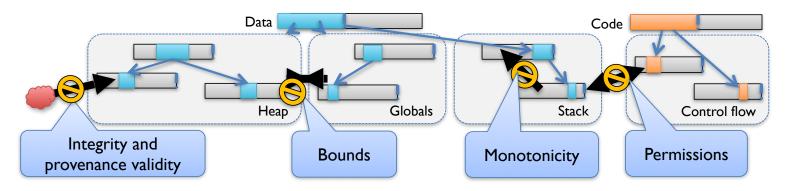

### Capability semantics applied to pointers

- Tags protect the integrity and provenance validity of pointers by:

- Constraining manipulation, detecting corruption, and preventing injection (e.g., via the network)

- Enabling accurate and deterministic detection, efficient tracking and revocation (i.e., temporal safety)

- **Bounds** prevent pointers from being used to access the wrong object (i.e., spatial safety)

- Monotonicity prevents pointer privilege escalation (e.g., broadening bounds)

- **Permissions** limit unintended use of pointers (e.g., W^X for pointers)

- Sealing prevents dereferencing, and enables non-monotonic domain transition

- → Deterministic, secrets-free memory protection and scalable software compartmentalization

### **CHERI MICROARCHITECTURE AND PROTOTYPES**

# Architectural primitives for software security

**Applications**

Systems software

Compilers and toolchain

Instruction-Set Architecture (ISA)

Microarchitecture

Software configures and uses capabilities to continuously enforce safety properties such as **referential**, **spatial**, **and temporal memory safety**, as well as higher-level security constructs such as **compartment isolation**

CHERI capabilities are an architectural primitive that compilers, systems software, and applications use to constrain their own future execution

The microarchitecture implements the capability data type and tagged memory, enforcing invariants on their manipulation and use such as capability bounds, monotonicity, and provenance validity

### CHERI demonstrated at a range of scales

Innovate UK

Mobile devices, data centers

Arm Morello application core + SoC, based on Neoverse NI 64-bit Arm-A baseline ISA Multicore, MMU-enabled, out-of-order core 2.5GHz CHERI-adapted FreeBSD, Linux, seL4, VxWorks OSes

Automotive, embedded, high-end IoT

Codasip X730 application core, based on A730 64-bit RISC-V baseline ISA Dual-issue, pipelined, with MMU CHERI-adapted FreeBSD, Linux, seL4 OSes

Microsoft CHERIOT Ibex microcontroller 32-bit RISC-V baseline ISA 3-stage pipeline, no MMU, 200-300MHz CHERIOT RTOS embedded OS

# Arm Morello (2022)

The Arm Morello Evaluation Platform—Validating CHERI-Based

Security in a High-Performance System

conventional architectures and the C/C++ codebase chronically prone to exploitable errors. The Capability Hardware Enhanced RISC Instructions (CHERI) research project has explored a novel architectural approach to ameliorate such issues using potential for mass-market adoption. This article describes the Morello Evaluation latform, covering the motivation and functionality of the Morello architectural ardware extensions; their potential for fine-grained memory safety and software ompartmentalization; formally proven security properties; impact on the architecture of the high-performance, out-of-order multiprocessor Arm Morello

- \$225M government, academia, and industrial research program led by UK Research and Innovation (UKRI)

- Announced partners: Arm, Google, Microsoft

- 15+ UK universities with research grants

- 70+ funded business incubation projects

- Baseline for design: Neoverse NI core

- 2.5GHz quad-core, superscalar

- Implements CHERI extensions

- Runs full CHERI-enabled software stacks

- Definitely a prototype, but a very powerful one!

- Roughly a thousand chips manufactured for use by research + development labs

# Microsoft CHERIoT core (2023)

### Comprehensive Formal Verification of Observational Correctness for the CHERIoT-Ibex Processor

tonychen@microsoft.com Microsoft Redmond, Washington, USA

San Diego, California, USA

antees that capabilities derived from other ca-root capabilities from —whether by a trusted mpiler, or application a be derived from an

tion of memory it can crucial non-increasing hardware and is what emory protection and

es had high memory sumption because the ssible memory region e number of bits as

ed by a sophisticated reatly improving the

optimisation comes at bounds combinations the microarchitecture ressed capabilities and

sions to RISC-V are

are formal verification are formal verification or a CHERI processor ation for the security I and authoritative ISA already available [8], the ISA design. The

nd authenticated ISA al barrier to applying

CHERI ISA extension

n of its implementa-l capabilities, presents d drive developments C-V base architecture presents a relatively l—formal verification

aim for more compre-

### CHERIoT: Complete Memory Safety for Embedded Devices

Cambridge, UK

Cambridge, UK

Robert N. M. Watson robert.watson@cl.cam.ac.uk University of Cambridge

The ubiquity of embedded devices is apparent. The desire for in-The ubiquity of embedded devices is apparent. In the desire for in-terest of the control of the desire for in-terest of the desired for i

To slake this need, we present a novel adaptation of the CHERI To alake this need, we present a novel adaptation of the CHEBI

republity architecture, co-designed with a green-field, accuritycentric RTOS. It is scaled for embedded systems, is capable of

lances for full inter-competitioner immorty safety. We highlight

central design decisions and offloads and summarize how our protoply RTOS uses these to enable memory—side, compartmentalized

applications. Unlike many state-of-the-art schemes, our solution

than the competition of the competitio nerabilities while maintaining source-level compatibility. W

Cambridge, UK

Mountain View, California, USA Hongyan Xia<sup>†</sup>\*

ACM Reference Format:

Saar Amar, David Chissall, Tony Chen, Nathaniel Wesley Filardo, Ber Lautte, Kumyan Liu, Robert Norton, Simon W. Moore, Tucong Tao, Robert N. M. Watton, and Hongyan Xia. 2023. CHEBST: Complete Memory Safety for Embedded Devices. In Seld-Annual IEEE/ACM International Symposium (2023). Topics of the Complete Memory Safety (2023).

### 1 INTRODUCTION

software stacks from different vendors. Even though researchers have disclosed an alarming number of memory vulnerabilities in recent years [6, 11, 15], the lessons learned from desktop and server systems do not directly translate to embedded systems. Page table techniques, sanitizers, dynamic

- CHERI-extended lbex microcontroller

- Microcontroller used in OpenTitan, etc.

- CHERI-RISC-V tuned for microcontrollers

- Clean-slate memory-safe, compartmentalized embedded OS

- CHERI extensions for revocation in SRAM

- Open sourced in February 2023

- Development a collaboration across Microsoft Research, MSRC, Azure Silicon, and Azure Edge + Platform

- Formal verification that microarchitecture implements specified ISA completed by Oxford University and University of Cambridge in 2025

- Now shipping in the lowRISC Sonata FPGA board, and being taped out for lowRISC/SCI Semiconductor ICENI board

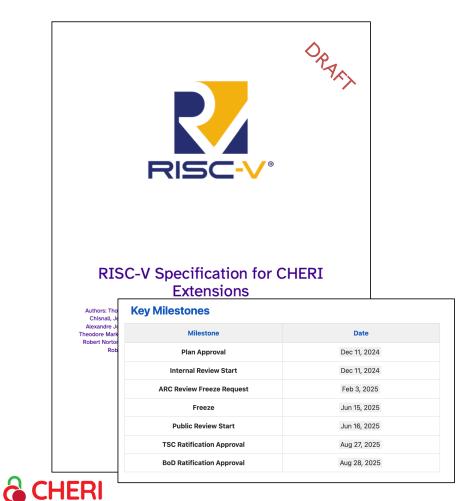

### CHERI-RISC-V standardization

- RISC-V International CHERI Special Interest Group (SIG) and Technical Group (TG)

- Co-chairs Alex Richardson (GChips), Simon Moore (Cambridge)

- Strong industrial engagement from multiple companies building products

- Incorporates both SRI/Cambridge baseline CHERI for application cores, and also Microsoft's CHERIOT extensions for microcontrollers

- Full draft specification now in review

- Ratification planned for August 2025

- Updated versions of CHERI LLVM, QEMU, ...

- Multiple processor designs targeting spec.

https://riscv.github.io/riscv-cheri/

### Current and arriving CHERI-RISC-V products

- Microsoft open-source CHERIoT-Ibex 32bit microcontroller core IP

- Google CHERI-enabled open-source ML accelerator prototype

- IowRISC CHERIOT-based Sonata FPGA board, ICENI FPGA board, ICENI SoC

- **SCI Semiconductor** CHERIoT-based ICENI SoC

- Secqai CHERI Ibex post-quantum crypto communications SoC

- Codasip proprietary 64-bit, MMU-enabled application core IP

- CapLtd open-source SystemVerilog CHERI CVA6 application core IP reference design

- **University of Cambridge** open-source research BSV cores: Piccolo, Flute, Toooba

Multiple test chips for CHERI-RISC-V silicon targeting 2025/2026

### **HOW SOFTWARE WORKS ON CHERI**

### Architectural primitives for software security

**Applications**

Systems software

Compilers and toolchain

Instruction-Set Architecture (ISA)

Microarchitecture

Software configures and uses capabilities to continuously enforce safety properties such as **referential**, **spatial**, **and temporal memory safety**, as well as higher-level security constructs such as **compartment isolation**

CHERI capabilities are an architectural primitive that compilers, systems software, and applications use to constrain their own future execution

The microarchitecture implements the capability data type and tagged memory, enforcing invariants on their manipulation and use such as capability bounds, monotonicity, and provenance validity

### Two key applications of the CHERI primitives

### Efficient, fine-grained memory protection for C/C++

- Strong source-level compatibility, but requires recompilation

- Deterministic and secret-free referential, spatial, and temporal memory safety

- Retrospective studies estimate 3/3 of memory-safety vulnerabilities mitigated

- Generally modest overhead (0%-5%, some pointer-dense workloads higher)

### 2. Scalable software compartmentalization

- Multiple software operational models from objects to processes

- Increases exploit chain length: Attackers must find and exploit more vulnerabilities

- Orders-of-magnitude performance improvement over MMU-based techniques (<90% reduction in IPC overhead in early FPGA-based benchmarks)

### **CHERI C/C++ MEMORY PROTECTION**

# What do we mean by C/C++ memory safety?

- Complex question, as while memory unsafety is clearly present, neither language defines what memory safety could mean

- Our thoughts from over a decade working on CHERI:

- **Memory safety** for C/C++ is (pragmatically) anything that would have defended you from memory-safety vulnerabilities

- Vulnerability mitigation deterministically coerces bugs that are currently vulnerabilities back into bugs i.e., you would no longer urgently patch them

- Exploit mitigation interferes with attack techniques that exploit memory unsafety

- **Deterministic mitigation** means that defenses always work regardless of information leakage, attempts to brute force, and so on

- Our ambition for CHERI C/C++ memory safety is to mitigate the vast majority (>70%)

of memory-safety vulnerabilities with full determinism

- Actual mitigation substantially exceeds this rate due to capabilities throughout the language runtime for exploit mitigation, but our field lacks methodology to evaluate this

Useful

definitions for

CHERI C/C++

defenses, but

also in

comparing to

other memorysafety

techniques

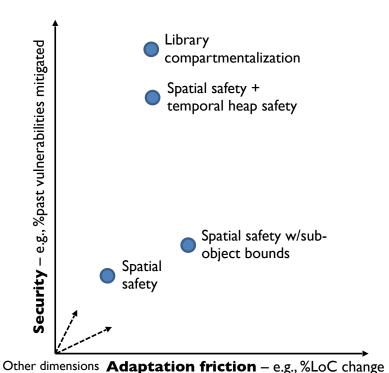

# A space of C memory-protection models

- C does not define a memory-protection model

- We have therefore had to (organically) grow one

- Optimization goals have been:

- Works well with CHERI (changing CHERI allowed, subject to PPA)

- %LoC source-code modification rates

- ABI / code-generation / optimization model alignment with status quo

- Dynamic performance overhead (e.g., cycles)

- Vulnerability mitigation (ideally deterministic)

- There is a rich space of potential memory-protection models

- Points combine (or not) different protection options

- E.g., Sub-object bounds, heap/stack temporal safety, ...

- Today's trade-off point hits around 70% of memory-safety vulnerabilities

- Compartmentalization shifts adversary model to arbitrary code execution

such as dynamic performance, PPA, CHERI alignment, ...

# Memory-safe CHERI C/C++

### Technical Report

UCAM-CL-TR-947 ISSN 1476-2986

Number 947

Computer Laboratory

CHERI C/C++ Programming Guide

Robert N. M. Watson, Alexander Richardson, Brooks Davis, John Baldwin, David Chisnall, Jessica Clarke, Nathaniel Filardo, Simon W. Moore, Edward Napierala, Peter Sewell, Peter G. Neumann

June 2020

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 https://www.cl.cam.ac.uk/

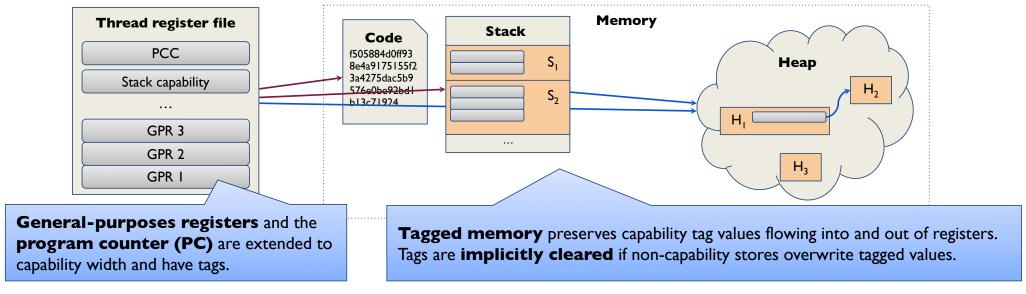

- Capabilities used to implement all pointers

Implied Control-flow pointers, stack pointers, GOTs, PLTs, ...

Explicit All C/C++-level pointers and references

- Strong referential, spatial, and heap temporal safety

- Minor changes to C/C++ semantics; e.g.,

- All pointers must have well defined single provenance

- Increased pointer size and alignment

- Care required with integer-pointer casts and types

- Memory-copy implementations may need to preserve tags

- Watson, et al. CHERI C/C++ Programming Guide, UCAM-CL-TR-947, June 2020

### Implementing C/C++ memory safety with CHERI (1/2)

- Whereas conventional C/C++ use integer pointers, CHERI C/C++ uses capability pointers

- C/C++ data types are laid out for wider capability-width, capability-aligned pointers

- Code generation is pointer-aware and uses explicit load/store-capability instructions

- Software TCBs restrict capability bounds and permissions as code runs

- Hardware continuously enforces capability protections on all pointer manipulation and use

### Implementing C/C++ memory safety with CHERI (2/2)

- Protections are applied to all pointer types in compiled code and the run-time environment:

- Implicit sub-language pointers such as GOT entries, stack pointers, return addresses

- Explicit language-level pointers to globals, stack and heap allocations, functions

- Software TCBs refine bounds and permissions during execution

- E.g., the mmap() system call, run-time linker, heap allocator, and stack allocator

### Implementing strong C/C++ memory protection with CHERI

| Property                       | Architectural representation                                                                                                                                                                                                                          | Software invariants                                                                                                                                                                                                                                            |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spatial safety                 | <ul> <li>Pointers implemented as capabilities</li> <li>Bounds, permissions refined by allocators and linkers to describe spatial constraints</li> </ul>                                                                                               | <ul> <li>Allocators and linkers maintain spatial mutual exclusion for all data types</li> <li>Alignment and padding for imprecise bounds</li> <li>free() uses rederivation if it relies on out-of-bounds accesses to reach metadata</li> </ul>                 |

| Control-<br>flow<br>protection | <ul> <li>Control-flow pointers implemented as capabilities</li> <li>Bounds, permissions refined by linkers, JITs to describe spatial constraints</li> <li>Sentry capabilities prevent mutation and dereference of pointers when not in PCC</li> </ul> | <ul> <li>Linkers, JITs maintains spatial mutual exclusion for all code pointers</li> <li>Alignment and padding for imprecise bounds</li> <li>Forward, backward, and exception edges protected</li> <li>Higher-level policies such as W^X as desired</li> </ul> |

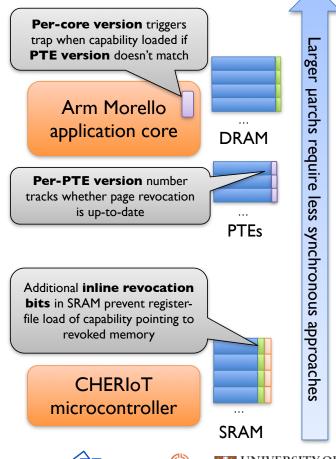

| Temporal safety                | <ul> <li>Load-barrier technique based on inline revocation bits (M-class cores) or CSR/PTE version bits (A-class cores) to implement atomicity, accelerate revocation</li> <li>Tag stripped on revocation</li> </ul>                                  | <ul> <li>Allocators, linkers, and JITs maintain temporal mutual exclusion</li> <li>Quarantine mechanism prevents reallocation before revocation, with strong atomicity</li> </ul>                                                                              |

### CHERI temporal safety

- Spatial safety maps naturally into capabilities ... how about temporal safety?

- The use-after-free problem maps into capability revocation problem

- Tags enable precise discovery and atomic revocation of capabilities

- Avoid architectural/microarchitectural indirection; instead use sweeping revocation to reliably find + invalidate capabilities

- Architectural load-barriers defer and amortize sweeping

- Prevent heap use-after-reallocation

- free() quarantines freed memory to defer, amortize sweeping costs

- Invariants guarantee no valid pointers to freed memory before reallocating

- Sweeps provide "snapshot at the start"-like view of revocation:

- In **microcontrollers**, checks can be synchronous (e.g., CHERIoT): Use **inline revocation bit** to check capabilities on load; clear tag if revoked

- In **application cores**, operate page at a time (e.g., Arm Morello): Use **per-page version** to trap on capability loads if may contain revoked pointers, reducing pause times and enabling lazy sweeping techniques

## Cornucopia Reloaded: Load barriers (ASPLOS 2024)

#### Cornucopia Reloaded: Load Barriers for CHERI Heap Temporal Safety Brett F. Gutstein

University of Cambridge

Peter Rugg

University of Cambridge

UK

Robert Norton

Microsoft

Nathaniel Wesley Filardo Microsoft Canada Jessica Clarke

University of Cambridge Mark Johnston

Simon W. Moore University of Cambridge UK

was its impractical "stop-the-world" pause times.

Violations of temporal memory safety ("use after free", "UAF")

continue to pose a significant threat to software security.

The CHERI capability architecture has shown promise as a

technology for C and C++ language reference integrity and spatial memory safety. Building atop CHERI, prior works – CHERIvoke and Cornucopia – have explored adding heap temporal safety. The most pressing limitation of Cornucopia

We present Cornucopia Reloaded, a re-designed drop-in replacement implementation of CHERI temporal safety, using a novel architectural feature – a per-page capability load

barrier, added in Arm's Morello prototype CPU and CHERI-RISC-V - to nearly eliminate application pauses. We analyze the performance of Reloaded as well as Cornucopia and CHERIvoke on Morello, using the CHERI-compatible SPEC CPU2006 INT workloads to assess its impact on batch

workloads and using pgbench and gRPC QPS as surrogate in-

teractive workloads. Under Reloaded, applications no longer

experience significant revocation-induced stop-the-world periods, without additional wall- or CPU-time cost over Cor-

nucopia and with median 87% of Cornucopia's DRAM traffic overheads across SPEC CPU2006 and < 50% for pgbench.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Alteracting with credit is permitted. To copy otherwise, or republish, to post on never no credit is permitted. To copy otherwise, or republish, to post on or serve. Request or cateful the to list, require prior perfect perfect permission and/or refer. Request

ASPLOS'24, April 27 - May 1, 2024, San Diego, CA, USA b 2024 Association for Computing Machinery. ACM ISBN 978-x-xxxx-xxxx-x/Y/MM...\$15.00 https://doi.org/10.1145/3620665.3640416

University of Cambridge UK Peter G. Neumann

Robert N. M. Watson SRI International USA University of Cambridge UK CCS Concepts: • Software and its engineering  $\rightarrow$  Soft-

ware safety; • Security and privacy → Operating systems security; • Hardware → Emerging architectures. Keywords: capability revocation, CHERI, temporal safety,

Ionathan Woodruff

University of Cambridge

Brooks Davis

SRI International

David Chisnall

SCI Semiconductor

Nathaniel Wesley Filardo, Brett F. Gutstein, Jonathan Woodruff, Jessica Clarke, Peter Rugg, Brooks Davis, Mark Johnston, Robert Nor on, David Chisnall, Simon W. Moore, Peter G. Neumann, and Robert N. M. Watson. 2024. Cornucopia Reloaded: Load Barriers for CHERI Heap Temporal Safety. In Proceedings of the 29th ACM International Teap Temporal satety. In Proceedings of the 29th A.M. International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS'24). ACM, New York, NY, USA, 18 pages. https://doi.org/10.1145/3620665.3640416

#### Introduction

Many programming languages offer an object-centric model of memory. New objects, initially unrelated to existing objects, are allocated on demand, used, and then released (implicitly and/or explicitly depending on the language). Low-ering the language's model to the underlying architecture, most often built around a coherent, integer-indexed array of memory words, is generally not fully-abstract; it becomes possible to @ confuse integers, object references, and memory indices that do not point to valid objects (such as those used internally by the memory allocator), risking reference in-tegrity violations; @ access adjacent objects, reaching beyond the bounds of a referenced object, violating spatial safety: and/or ® access an object after its life ended ("use-after-free" "UAF") or after the underlying memory has been repurposed These affordances beyond the programmer's intent continue to pose a significant threat to software security [17, 35], and Cornucopia heap temporal safety (IEEE SSP 2020), is a GC-inspired, quarantining technique

- The kernel VM system tracks "capability dirty" pages

- A long "stop-the-world" phase as much as 30 milliseconds measured in practice

- Cornucopia Reloaded (ASPLOS 2024) moves to a GC-inspired "load-barrier"

- VM invariant is that accessible pages have already undergone revocation

- Depend on I-bit capability generation added to VM PTEs, implemented by Morello

- Stop-the-world pauses tens of microseconds

- Enabled by default since CheriBSD 23.11

## Microsoft security analysis of CHERI C/C++

#### SECURITY ANALYSIS OF CHERLISA

Nicolas Joly, Saif ElSherei, Saar Amar - Microsoft Security Response Center (MSRC)

#### INTRODUCTION AND SCOP

The CHERI ISA extension provides memory-protection features which allow historically memory-unsafe programming languages such as C and C++ to be adapted to provide strong, compatible, and efficient protection against many currently widely exploited vulnerabilities.

CHERI requires addressing memory through unforgeable, bounded references called capabilities. These capabilities are 128-bit extensions of traditional 64-bit pointers which embed protection metadata for how the pointer can be dereferenced. A separate tage table is maintained to distinguish each capability word of physical memory from non-capability data to enforce unforgeability.

In this document, we evaluate attacks against the pure-capability mode of CHERI since non-capability code in CHERI's hybrid mode could be attacked as-is-dough. The CHERI system assessed for this research is the CheriBSD operating system running under QEMU as it is the largest CHERI adapted software available to dough.

CHERI also provides hardware features for application compartmentalization [18]. In this document, we will review only the memory safety guarantees, and show concrete examples of exploitation primitives and techniques for various classes of vulnerabilities.

#### SUMMA

CHERI's ISA is not yet stabilized. We reviewed the current revision 7, but some of the protections such as executable pointer sealin is still experimental and likely subject to future change.

The CHERI protections applied to a codebase are also highly dependent on compiler configuration, with stricter configurations requiring more refactoring and qualification testing (highly security-critical code can opt into more guarantees), with the strict sub-allocation bounds behavior being the most likely high friction to enable. Examples of the protections that can be configured include:

- Pure-capability vs hybrid mode

- Chosen heap allocator's resilience

- Sub-allocation bounds compilation flag

Linkage model (PC-relative, PLT, and per-function .captable)

- Extensions for additional protections on execute capabilities

- Extensions for temporal safety

However, even with enabling all the strictest protections, it is possible that the cost of making existing code CHERI compatible will be less than the cost of rewriting the code in a memory safe language, though this remains to be demonstrated.

We conservatively assessed the percentage of vulnerabilities reported to the Microsoft Security Response Center (MSRC) in 2019 and found that approximately 31% would no longer pose a risk to customers and therefore would not require addressing through a security update on a CHERI system based on the default configuration of the CheniBSD operating system. If we also assume that automatic initialization of stack variables (Initial) and of heap allocations (e.g. pool zeroing) is present, the total number of vulnerabilities deterministically mitigated exceeds 43% with additional features such as Comucopia that help prevent temporal safety issues such as use after free, and assuming that it would cover 80% of all the UAFs, the number of deterministically mitigated vulnerabilities would be at least 67%. There is additional work that needs to be done to protect the stack and add fined grained CFI, but this combination means CHERI looks very promising in its early stages.

Microsoft Security Response Center (MSRC)

1 | Page

- Microsoft Security Response Center (MSRC) study analyzed all 2019 Microsoft critical memory-safety security vulnerabilities

- Metric: "Poses a risk to customers → requires a software update"

- Vulnerability mitigated if no security update required

- Blog post and 42-page report

- Concrete vulnerability analysis for spatial safety

- Abstract analysis of the impact of temporal safety

- Red teaming of specific artifacts to gain experience

- CHERI, "in its current state, and combined with other mitigations, it would have **deterministically mitigated at least two thirds** of all those issues"

## **CHERI SOFTWARE** COMPARTMENTALISATION

## What is software compartmentalization?

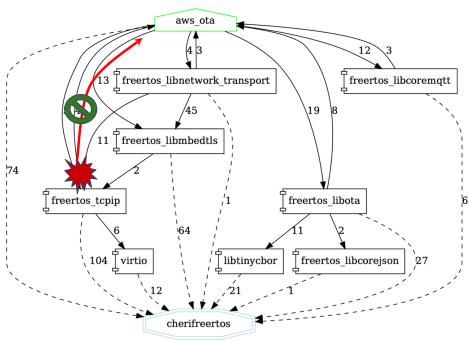

CheriFreeRTOS components and the application execute in compartments. CHERI contains an attack within TCP/IP compartment, which access neither flash nor the internals of the software update (OTA) compartment.

- Fine-grained decomposition of a larger software system into **isolated modules** to constrain the impact of faults or attacks

- Goals is to minimize privileges yielded by a successful attack, and to limit further attack surfaces

- Usefully thought about as a graph of interconnected components, where the attacker's goal is to compromise nodes of the graph providing a route from a point of entry to a specific target

## Compartmentalization built on CHERI memory safety

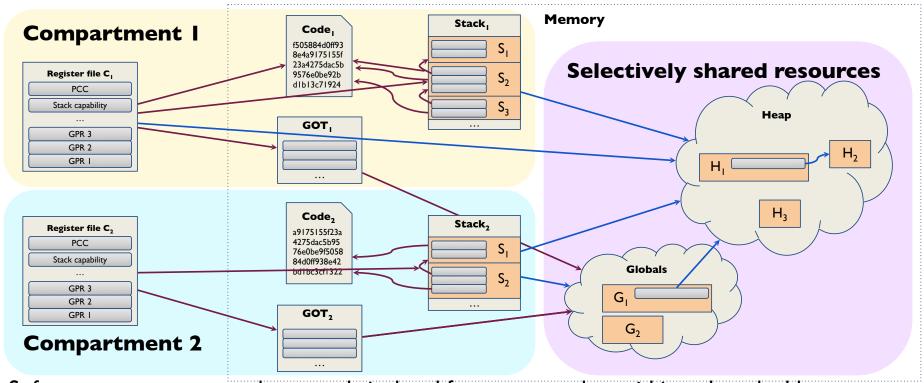

- Software components can be strongly isolated from one another within a shared address space Initial sharing is authorized by the TCB (functions, globals, ...) by delegating capabilities Fast switching, shared memory w/o TLB contention, capability delegation accelerate sharing

## Compartmentalization scalability

- CHERI dramatically improves compartmentalization scalability

- More compartments

- More frequent and faster domain transitions

- Faster shared memory between compartments

- Many potential use cases e.g., sandbox processing of each image in a web browser, processing each message in a mail application

Early benchmarks show a 1-to-2 order of magnitude performance inter-compartment communication improvement compared to conventional designs

### Two promising CHERI-based compartmentalization models

#### Library compartmentalization (c18n)

- Reuse existing library (or library subset) abstractions

- Existing memory-safe linkage as foundation

- Interpose domain-transition trampolines on PLT calls

- Separate per-compartment stacks

- Policy language enables sub-library boundaries to be used

#### **UNIX co-located processes (co-processes)**

- Multiple processes in each address space, separate by CHERI

- Kernel protrudes fast domain-transition switcher into userlevel

- Inter-process shared memory shares TLB entries

- Measured I-2 orders of magnitude performance vs. IPC

Shipped in CheriBSD 22.12.

Updates in 23.11, 24.05, and 25.03.

Prototype running; targeted for inclusion in a 2026 CheriBSD release.

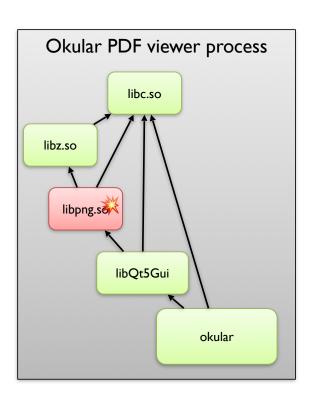

## CHERI library compartmentalization (c18n)

**Libraries** are software-engineering boundaries around code

• E.g., libz (decompression) and libpng (PNG processing)

**Compartmentalization** limits access to global state, control flow:

- Control-flow protection for cross-compartment calls

- **Granular delegation of access** to global variables and functions from other libraries based on link-time policy

- Prevents direct use of system calls and kernel sérvices

- Prevents integrity, confidentiality, and control-flow crosscompartment attacks via stacks

- Dynamically grants further rights to resources (e.g., heap allocations, function pointers, ...) via **pointer delegation**

Support for library compartmentalization has shipped in multiple CheriBSD releases and is experimental but very usable

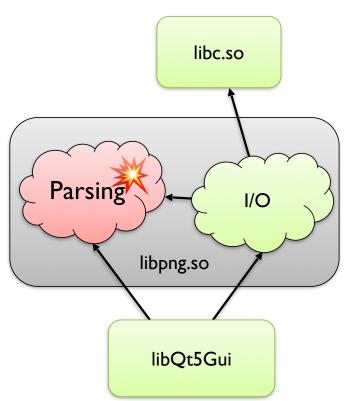

## CHERI sub-library compartmentalization

However, sometimes software engineering boundaries aren't the right security boundaries; e.g.,

- libpng is vulnerable when processing malicious data ...

- ... but some libpng APIs requires file-system access

**Sub-library compartmentalization** allows compartment boundaries to differ from library boundaries without refactoring

- Subdivide library state, library code, and access requirements into multiple compartments within library

- · Compromise in one component in a library (e.g., image parsing) need not imply compromise of another (e.g., I/O)

**Experimental feature in April 2025 CheriBSD release**

## Sub-library compartment approach

**Sub-library compartments** are contiguous code, data, and linkage that can access only authorized resources:

- New ELF metadata specifies compartment details including name and Program-Counter Capability (PCC) bounds

- External functions and globals are reached via per-compartment Global Offset Tables (GOTs), reached via each compartment's PCC

The runtime also applies appropriate stack isolation, control-flow, and other protections to sub-library compartments

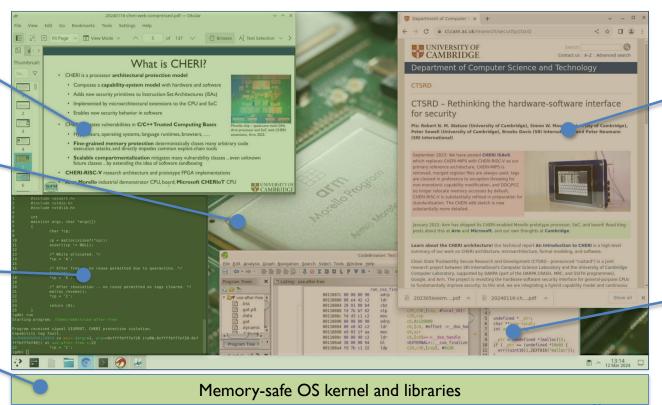

## **OPERATING-SYSTEM SUPPORT: CHERIBSD RESEARCH OS**

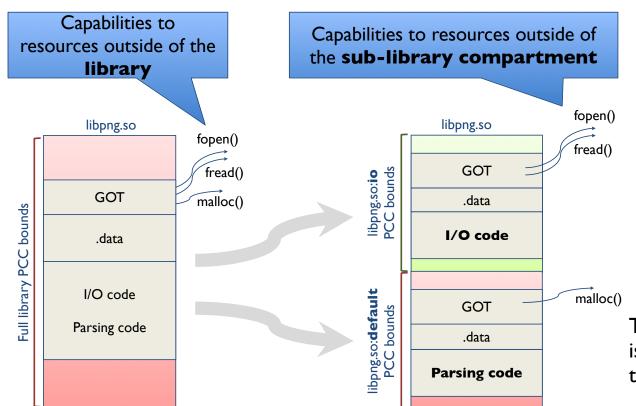

## CheriBSD research operating system

**CheriBSD** is a FreeBSD-based research operating system designed to explore OS use of CHERI:

- Incrementally deployed use of CHERI: Not a clean-slate OS design!

- Universal use of CHERI: Ubiquitous memory safety and compartmentalization

- 14 years of hardware-software co-design alongside CHERI architecture and the CHERI compiler, driving critical design choices throughout CHERI architecture and microarchitecture

- New OS design principles that themselves are systems research contributions, and are generalizable to other systems (e.g., CHERI-seL4 and CHERI Linux being developed currently)

https://cheribsd.org

#### **Features**

Spatial and temporal memory safety for userspace and spatial memory safety for the kernel

Memory-safe KDE-based graphical desktop stack (Morello-only)

CHERI-enabled "bhyve"

hypervisor for capability-aware

guest OSes (Morello-only)

Userspace and kernel debugger support for memory-safe and memory-unsafe code

Compatible with existing memory-unsafe 64-bit applications

Experimental library-based compartmentalisation (coprocesses and kernel modules in development)

Pre-built USB stick image with interactive guided installer

10,000+ pre-built memory-safe packages and 26,000+ pre-built memory-unsafe packages

Runs on Morello boards, Morello FVP, QEMU and FPGA

## A PROTOTYPE SOFTWARE ECOSYSTEM FOR DEMONSTRATION AND EVALUATION

## CHERI prototype software stack

**Complete CHERI-enabled open-source software stack** from bare metal up: compilers/toolchain, debugger, hypervisor, OS, and applications to evaluate, demonstrate 100+ MLoC of memory-safe CHERI C/C++ with incremental adoption path:

**Open-source application suite** (KDE Plasma, Wayland, WebKit, Python, OpenSSH, nginx, ...)

**CheriBSD** (funded by DARPA and UKRI) (Arm Morello and CHERI-RISC-V)

- FreeBSD kernel + userspace, application stack

- Kernel spatial and referential safety

- Userspace spatial, referential, and temporal safety

- User library compartmentalization

- Co-process compartmentalization (in development)

- CHERI-enabled bhyve Type-2 hypervisor (Morello only)

- Over 10K memory-safe, precompiled third-party userlevel software packages

- 64-bit binary compatibility for legacy binaries on Morello and

#### Linux

(Arm Morello Linux → CHERI Linux in collaboration with Codasip, Arm / Linaro, CapLtd)

CHERI Clang/LLVM compiler suite, Morello GCC, LLD, LLDB, GDB

## 2021 desktop pilot study results

#### Developed:

- 6 million lines of C/C++ code compiled for memory safety; modest dynamic testing

- Three compartmentalization whiteboard case studies in Qt/KDE

#### **Evaluation results:**

- 0.026% LoC modification rate across full corpus for memory safety

- **73.8% mitigation rate** across full corpus, using memory safety and compartmentalization

Useful observation to be made about memory safety: Not enough to address the de facto threat model of quite a few libraries ...

## 2024.05 Morello memory-safe desktop stack

## 50-100MLoC of memory-safe C/C++ on a shipping Arm Morello prototype board today:

- CheriBSD kernel with DRM + Panfrost drivers

- CheriBSD userspace with libraries and tools

- Plasma, KDE base applications including Dolphin, Okular, Kate, and Konsole

- Library compartmentalization of all memory-safe userlevel components

- Rich software development environment including Clang/LLVM, GDB, Ghidra, ...

- Roughly 10K memory-safe third-party software packages, and 20K aarch64 packages

- Also includes memory-safe server software such as gRPC, nginx, postgres, ...

Some more complex, un-adapted applications (e.g., Chromium, OpenJDK) run in 64-bit Arm mode

## CHERI and legacy applications side-by-side on Morello

#### **Enables incremental application migration to memory safety**

Memory-safe PDF viewer

Memory-safe desktop environment

Memory-safe terminal window and commands

Memory-safe OS kernel

Legacy 64-bit Arm Chromium browser

Legacy 64-bit Arm JVM

## **DEMONSTRATION**

## Grand challenge application: Google Chromium

- Foundation for Google Chrome, Microsoft Edge, Microsoft Teams, Electron, ...

- ~27MLoC base source code with (at least) 7 compilers, of which 6 are Just-In-Time compilers (JITs)

- ~47MLoC including >760 library dependencies

- V8, an intimidatingly real runtime for JavaScript and WASM (~2MLoC)

- Code from diverse origins and in idiomatic C and C++

- Vast wealth of past vulnerabilities to use in evaluation (~I critical memory-safety vulnerability every 2 days in 2023)

- Performance critical components, especially V8

- Chromium able to browse increasingly complex web sites

- Roughly 18 staff months of effort so far; close to functional browsing

- o .. but .. compare to size of 100-member Chromium security team!

- Chromium base (27MLoC) ~0.045% LoC change; V8 (2MLoC) ~0.8% LoC change

- Pilot project funded by UKRI and Google

Chromium

## Chromium demo: CVE-2023-4863 ("BLASTPASS")

CHERI deterministically mitigates this Chromium vulnerability without any awareness about the nature, location, or origin of the vulnerability during development.

This memory-safety vulnerability was discovered "in the wild" following targeted attacks against victims in the US using NSO Group's Pegasus:

- Naturally occurring vulnerability in Google's libwebp image library

- Heap-memory buffer overflow exploitable for remote arbitrary code execution

- Undiscovered for years despite fuzzing due to complexity of Huffman coding logic

- Affected Chrome, Edge, and WebKit

- Ist-party code for Google

- 3rd-party for Apple and Microsoft

- Zero interaction exploitation of Apple iOS

- No prior awareness of this CVE in our work

- 0% LoC changes to webp for use on CHERI

## CONCLUSION

## Ease of adoption compared to high-level languages

| Language | Approximate open-source LoC* | Memory safe      |

|----------|------------------------------|------------------|

| С        | 10,317,799,775               | X → ✓ with CHERI |

| C++      | 2,937,552,905                | X → ✓ with CHERI |

| Java     | 2,614,800,470                | ✓                |

| Rust     | 39,538,172                   | ✓                |

Worth pondering: In just the past 18 months, a small research team at SRI, Cambridge, and CapLtd has adapted ~I50MLoC of C++ for CHERI memory safety

# Could we achieve practical memory safety\* for multi-BLoC C/C++ software stacks within 4 years without a ground-up rewrite?

\*There's a **very** long discussion to have about what "memory-safe C/C++" means, but Microsoft's practical definition of "deterministically mitigates security vulnerabilities" seems a good place to start.

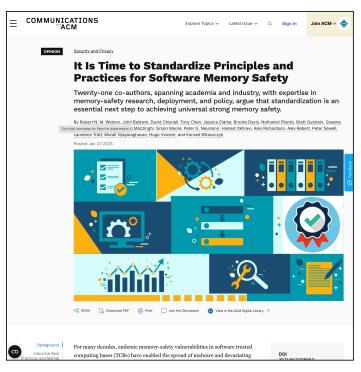

# It is Time to Standardize Principles and Practices for Software Memory Safety (CACM Feb 2025)

- 20 coauthors including from Arm, Microsoft, and Google.

- Reflects on maturing strong memory-safety techniques for lower-level TCBs

- Memory-safe systems languages

- Architectural techniques such as CHERI

- Formal methods

- The lack of a clear way to express memory-safety requirements impedes demand signals from government industry, limits policy interventions

- E.g., no consistent understanding of ideas around completeness and determinism – e.g., "CHERI" vs "PAC and MTE"

- Recognize and encourage current best practices while creating a tool to incentivize adoption of strong memory-safety techniques

- ETSITC CYBER kicked off an effort to establish core memory-safety definitions as of August 2025 – first in-person meeting September 2025

## (Draft) definitions for memory safety

Work-inprogress

- Strong memory safety is memory safety that must be:

- Deterministic Not dependent on secrets that may be leaked or brute forced

- Complete Implements referential, spatial, temporal, and control-flow memory safety

- **Concurrency safe** Memory safety is enforced in the presence of concurrency

- Strong memory safety is memory safety that may support:

- Compartmentalisation Retains memory safety in the presence of code compiled with an untrustworthy compiler

- Memory-safe sub-allocators Enables extensible memory allocation

- A memory-safety TCB Depends only on code that is, itself, memory safe

- **General concurrency safety** Strong concurrency properties for all memory accesses

- **Weak memory safety** incompletely implements required strong memory-safety properties e.g., is probabilistic or secrets based, omits strong control-flow protections, etc.

## CHERI Alliance

- Support a collaborative community around CHERI from industry, academia, government

- Foster community open-source projects

CHERI LLVM, CHERI QEMU, CHERI-seL4, CHERI Linux, test suites, etc.

- Develop documentation, tutorials, standards, and promotional material about CHERI

- Distribute reference hardware to open-source and other developers (e.g., of Arm Morello, lowRISC Sonata boards)

- Host conferences and other events

Launched in November 2024 and membership growing as companies continue to come on board

## Learning more about CHERI

Read our article in the 2024 special issue of IEEE Security and Privacy Magazine:

CHERI: Hardware-Enabled C/C++ Memory Protection at Scale

• See our technical reports for great detail:

Introduction to CHERI

CHERI C/C++ Programming Guide

CHERI ISA Specification

And see our research papers on everything from microarchitectural implementations of tagged memory to the implications of memory safety for the UNIX process model

CHERI: Hardware-Enabled C/C++ Memory Protection at Scale. IEEE Security & Privacy, vol. 22, no. 04, pp. 50-61, July-August 2024.

## Conclusion

- New architectural primitives enable fine-grained C/C++ memory protection and scalable software compartmentalization

- Ideas portable across a range of architectures (Arm, RISC-V, ...) with full-scale software stacks running on them

- Prototype Arm Morello board shipped in 2022

- Open-source Microsoft CHERIoT microcontroller released in 2023; this and other CHERI-RISC-V cores to appear in ASIC products over the next year

- Large-scale software demonstrators starting to come to fruition, with I50MLoC of C/C++ including early Chromium/V8 adaptation

- Large and active research ecosystem spanning companies that include Arm, Google, Microsoft, HP, and many others

http://www.cheri-cpu.org/